#### **Features**

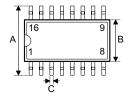

• 16-pin SOP package

## **General Description**

This ASIC is designed to reduce the discrete logics used in the mother board. With this device, the mother board's reliability is increased, while its size and cost are reduced.

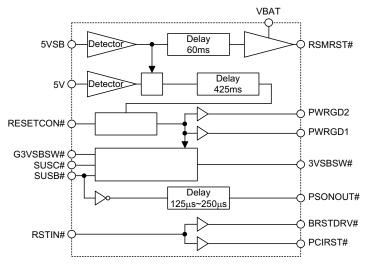

The function of this device is to regulate the power control of the mother board. The RSMRST# signal is used to identify the status of the 5VSB. The 3VSBSW# signal

is used to select the 3.3V power source. The PWRGD1 and PWRGD2 signals are used to indicate whether the power is OK or not. The PSONOUT# signal is used to control the On and Off of the power supply. The BRSTDRV# and PCIRST# signals are used to reset the devices.

## **Block Diagram**

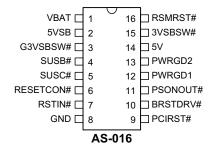

# **Pin Assignment**

# **Pin Description**

| Pin No.                       | Pin Name       | I/O Spec.                                                                                      | Description                                                                                                                                                                                                                                                                                         |  |

|-------------------------------|----------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power & reset control: 8 pins |                |                                                                                                |                                                                                                                                                                                                                                                                                                     |  |

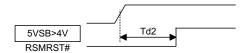

| 16                            | RSMRST#        | @VDD=VBAT (3.3V) O/P spec: NMOS OD I <sub>OL</sub> =4mA/0.4V Pull-high 5V tolerance            | This is the +5VSB power good signal, with Schmitt trigger input, the high threshold is $4V\pm0.2V$ , and the low threshold is $3.5V\pm0.2V$                                                                                                                                                         |  |

| 6                             | RESETCON#      | @VDD=5VSB I/P spec: TTL input Internal pull-high 100kΩ to 5VSB                                 | This pin connects to the reset button, and also to the other r set source on the motherboard.  Low reset chip (5V logic)  PWRGD follows with RESETCON                                                                                                                                               |  |

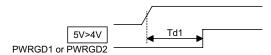

| 12                            | PWRGD1         | @VDD=5VSB<br>O/P spec: NMOS OD<br>I <sub>OL</sub> =10mA/0.4V                                   | 5V>4volt, wait for 425ms then rising PWRGD to high 5V<3.5volt, then falling PWRGD to low This pin also follows with RESETCON                                                                                                                                                                        |  |

| 13                            | PWRGD2         | @VDD=5VSB<br>O/P spec: NMOS OD<br>I <sub>OL</sub> =10mA/0.4V                                   | 5V>4volt, wait for 425ms then rising PWRGD to high 5V<3.5volt, then falling PWRGD to low This pin also follows with RESETCON                                                                                                                                                                        |  |

| 7                             | RSTIN#         | @VDD=VDD5VSB<br>I/P spec: TTL input<br>Internal pull-high<br>100kΩ to 5VSB                     | Original Reset signal from chipset                                                                                                                                                                                                                                                                  |  |

| 9                             | PCIRST#        | @VDD=VDD5VSB<br>O/P spec: CMOS O/P<br>I <sub>OL</sub> =16mA/0.4V<br>I <sub>OH</sub> =16mA/4.5V | Reset for add-on PCI card                                                                                                                                                                                                                                                                           |  |

| 10                            | BRSTDRV#       | @VDD=VDD5VSB<br>O/P spec: CMOS O/P<br>I <sub>OL</sub> =16mA/0.4V<br>I <sub>OH</sub> =16mA/4.5V | Reset for IDE                                                                                                                                                                                                                                                                                       |  |

| 11                            | PSONOUT#       | @VDD=5VSB<br>O/P spec: NMOS OD<br>I <sub>OL</sub> =10mA/0.4V                                   | PSON# signal to power supply PSONOUT#= NOT (SUSB#) Propagation delay=125µs~250µs                                                                                                                                                                                                                    |  |

| Suspend                       | control: 4 pin | 1                                                                                              |                                                                                                                                                                                                                                                                                                     |  |

| 4                             | SUSB#          | @VDD=5VSB I/P spec: TTL input Internal pull-high 100kΩ to 5VSB                                 | SUSB# signal from Intel/VIA South Bridge. High at S0~S2 and turn low when S3/S4/S5                                                                                                                                                                                                                  |  |

| 5                             | SUSC#          | @VDD=5VSB I/P spec: TTL input Internal pull-high 100kΩ to 5VSB                                 | SUSC# signal from Intel/VIA South Bridge. High at S0~S3 and turn low when S4/S5                                                                                                                                                                                                                     |  |

| 15                            | 3VSBSW#        | @VDD=5VSB<br>O/P spec: CMOS O/P<br>I <sub>OL</sub> =4mA/0.4V<br>I <sub>OH</sub> =4mA/4.5V      | Active low when system enters the S3 state until system enters the S0 state and PWRGD is active high                                                                                                                                                                                                |  |

| 3                             | G3VSBSW#       | @VDD=5VSB<br>I/P spec: TTL input<br>Internal pull-low<br>100kΩ to GND                          | Signal used for gating off 3VSBSW# Low: Gating off 3VSBSW# (default, BIOS will program low when power on) High: not gating off 3VSBSW# (BIOS will program high before entering S3 state) This signal will be transparent while PWRGD is high internally and latched with the falling edge of SUSB#. |  |

| Pin No. | Pin Name  | I/O Spec. | Description |

|---------|-----------|-----------|-------------|

| Power/G | ND: 4 pin |           |             |

| 14      | 5V        | Power     |             |

| 2       | 5VSB      | Power     |             |

| 1       | VBAT      | Power     |             |

| 3       | GND       | GND       |             |

# **Absolute Maximum Ratings**

| Supply Voltage0.3V to 5.5V                                  | Storage Temperature50°C to 125°C   |

|-------------------------------------------------------------|------------------------------------|

| Input VoltageV <sub>SS</sub> -0.3V to V <sub>DD</sub> +0.3V | Operating Temperature–25°C to 70°C |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

## **D.C. Characteristics**

Ta=25°C, VDD5V=5V, VDD5VSB=5V, VBAT=3.3V

| Pin Name                     | Symbol          | I/O Spec. & Test Condition        | Min. | Тур. | Max. | Unit |

|------------------------------|-----------------|-----------------------------------|------|------|------|------|

| VDAT                         | I <sub>OP</sub> | VDD5VSB=5V, VDD5V=5V              | _    | _    | 5    | μА   |

| VBAT                         | I <sub>SB</sub> | VDD5VSB=0V, VDD5V=0V              | _    | _    | 1    | μА   |

| \/DDE\/CD                    | I <sub>OP</sub> | VBAT=3.3V, VDD5V=5V               | _    | _    | 5    | mA   |

| VDD5VSB                      | I <sub>SB</sub> | VBAT=3.3V, VDD5V=0V               | _    | _    | 1    | mA   |

| VDD5V                        | I <sub>OP</sub> | VBAT=3.3V, VDD5V=5V               | _    | _    | 5    | mA   |

| RSMRST#                      | I <sub>OL</sub> | VBAT=3.3V, V <sub>OL</sub> =0.4V  | 4    | 6    | _    | mA   |

| RESETCON#                    | V <sub>IL</sub> | VDD5VSB=5V                        | 0    | _    | 0.8  | V    |

| RSTIN#<br>SUSB#              | V <sub>IH</sub> | VDD5VSB=5V                        | 2    | _    | 5    | V    |

| SUSC#                        | R <sub>H</sub>  | VDD5VSB=5V, V <sub>IL</sub> =0V   | 60   | 100  | 150  | ΚΩ   |

|                              | V <sub>IL</sub> | VDD5VSB=5V                        | 0    | _    | 0.8  | V    |

| G3VSBSW#                     | V <sub>IH</sub> | VDD5VSB=5V                        | 2    | _    | 5    | V    |

|                              | R <sub>L</sub>  | VDD5VSB=5V, V <sub>IH</sub> =5V   | 85   | 125  | 165  | ΚΩ   |

| 0) (0 D 0) 4                 | I <sub>OL</sub> | VDD5VSB=5V, V <sub>OL</sub> =0.4V | 4    | _    | _    | mA   |

| 3VSBSW#                      | I <sub>OH</sub> | VDD5VSB=5V, V <sub>OH</sub> =4.5V | 4    | _    | _    | mA   |

| PWRGD1<br>PWRGD2<br>PSONOUT# | I <sub>OL</sub> | VDD5VSB=5V, V <sub>OL</sub> =0.4V | 10   | _    | _    | mA   |

| PCIRST#                      | I <sub>OL</sub> | VDD5VSB=5V, V <sub>OL</sub> =0.4V | 16   | _    | _    | mA   |

| BRSTDRV#                     | I <sub>OH</sub> | VDD5VSB=5V, V <sub>OH</sub> =4.5V | 16   | _    | _    | mA   |

## A.C. Characteristics

Ta=25°C, VDD5V=5V, VDD5VSB=5V, VBAT=3.3V

| Symbol | Parameter        | Min. | Тур. | Max. | Unit |

|--------|------------------|------|------|------|------|

| Td1    | Power Good Delay | 300  | 425  | 600  | ms   |

| Td2    | RSMRST# Delay    | 40   | 60   | 90   | ms   |

Power good delay

• RSMRST# delay

# **Timing Diagrams**

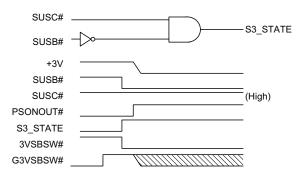

## From S0 to S3 (SW off to on)

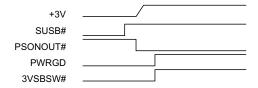

# From S3 to S0 (SW on to off)

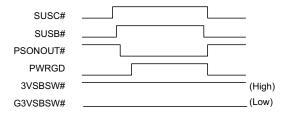

## From S5 to S0 and from S0 to S5 (not SW on)

# **Package Information**

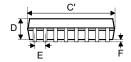

16-pin NSOP (150mil) outline dimensions

| Cumbal | Dimensions in mil |      |      |  |

|--------|-------------------|------|------|--|

| Symbol | Min.              | Nom. | Max. |  |

| Α      | 228               | _    | 244  |  |

| В      | 149               | _    | 157  |  |

| С      | 14                | _    | 20   |  |

| C'     | 386               | _    | 394  |  |

| D      | 53                | _    | 69   |  |

| Е      | _                 | 50   | _    |  |

| F      | 4                 | _    | 10   |  |

| G      | 22                | _    | 28   |  |

| Н      | 4                 | _    | 12   |  |

| α      | 0°                | _    | 10°  |  |

# **Product Tape and Reel Specifications**

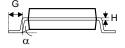

# Reel dimensions

SOP 16N

| Symbol | Description           | Dimensions in mm |  |  |

|--------|-----------------------|------------------|--|--|

| Α      | Reel Outer Diameter   | 330±1.0          |  |  |

| В      | Reel Inner Diameter   | 62±1.5           |  |  |

| С      | Spindle Hole Diameter | 12.75+0.5        |  |  |

| D      | Key Slit Width        | 1.5+0.15         |  |  |

| T1     | Space Between Flange  | 16.4+0.2         |  |  |

| T2     | Reel Thickness        | 22.4+0.4         |  |  |

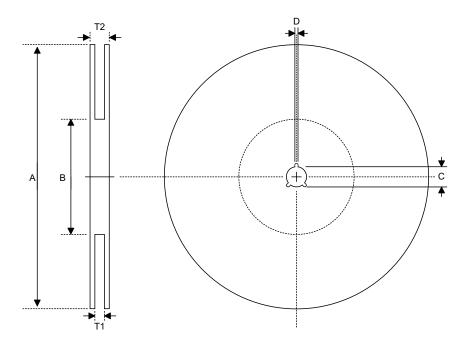

## Carrier tape dimensions

SOP 16N

| Symbol | Description                              | Dimensions in mm |

|--------|------------------------------------------|------------------|

| W      | Carrier Tape Width                       | 16.0±0.3         |

| Р      | Cavity Pitch                             | 8.0±0.1          |

| E      | Perforation Position                     | 1.75±0.1         |

| F      | Cavity to Perforation (Width Direction)  | 7.5±0.1          |

| D      | Perforation Diameter                     | 1.55+0.1         |

| D1     | Cavity Hole Diameter                     | 1.5+0.25         |

| P0     | Perforation Pitch                        | 4.0±0.1          |

| P1     | Cavity to Perforation (Length Direction) | 2.0±0.1          |

| A0     | Cavity Length                            | 6.5±0.1          |

| В0     | Cavity Width                             | 10.3±0.1         |

| K0     | Cavity Depth                             | 2.1±0.1          |

| t      | Carrier Tape Thickness                   | 0.3±0.05         |

| С      | Cover Tape Width                         | 13.3             |

Holtek Semiconductor Inc. (Headquarters) No.3, Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan

Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

## Holtek Semiconductor Inc. (Sales Office)

11F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan

Tel: 886-2-2782-9635 Fax: 886-2-2782-9636

Fax: 886-2-2782-7128 (International sales hotline)

# Holtek Semiconductor (Shanghai) Inc.

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China

Tel: 021-6485-5560 Fax: 021-6485-0313 http://www.holtek.com.cn

## Holtek Semiconductor (Hong Kong) Ltd.

RM.711, Tower 2, Cheung Sha Wan Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong Kong

Tel: 852-2-745-8288 Fax: 852-2-742-8657

#### Holmate Semiconductor, Inc.

48531 Warm Springs Boulevard, Suite 413, Fremont, CA 94539

Tel: 510-252-9880 Fax: 510-252-9885 http://www.holmate.com

#### Copyright © 2002 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.