An ISO/TS 16949 and ISO 9001 Certified Company

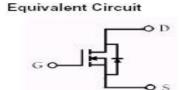

### NPN CHANNEL ENHANCEMENT MODE FIELD EFFECT TRANSISTOR

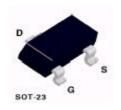

G : Gate S : Sourse D : Drain 2N7002

PIN COFIGURATION

G= GATE

S= SOURCE D= DRAIN SOT-23 Formed SMD Package

Marking 2N7002=S72

**Designed for High Speed Pulse Amplifier and Drive Application**

ABSOLUTE MAXIMUM RATINGS (T<sub>a</sub>=25°C unless specified otherwise)

| DESCRIPTION                                         | SYMBOL          | VALUE        | UNITS |

|-----------------------------------------------------|-----------------|--------------|-------|

| Drain Source Voltage                                | $V_{DSS}$       | 60           | V     |

| Drain Gate Voltage                                  | $V_{DRG}$       | 60           | V     |

| Gate Source Voltage                                 | $V_{GSS}$       | 20           | V     |

| Maximum Drain Current Continuous                    | I <sub>D</sub>  | 200          | mA    |

| Maximum Drain Current Pulse                         | *I <sub>D</sub> | 800          | mA    |

| Maxium Power Dissipation Derating Above 25⁰C        | $P_D$           | 350          | mW    |

| Operating and Storage Junction<br>Temperature Range | $T_{j},T_{stg}$ | - 55 to +150 | °C    |

#### THERMAL RESISTANCE

| Junction to Ambient in free air | $R_{th}$ (i-a) | 357 | °C/W |

|---------------------------------|----------------|-----|------|

#### ELECTRICAL CHARACTERISTICS (T<sub>a</sub>=25°C unless specified otherwise)

| DESCRIPTION                       | SYMBOL                | TEST CONDITION                             | MIN | TYP | MAX   | UNITS |

|-----------------------------------|-----------------------|--------------------------------------------|-----|-----|-------|-------|

| Drain Source Breakdown Voltage    | $V_{DSS}$             | $V_{GS}$ =0V, $I_D$ =10 $\mu$ A            | 60  |     |       | V     |

| Zero Gate Voltage Drain Current   | I <sub>DSS</sub>      | V <sub>DS</sub> =60V, V <sub>GS</sub> =0   |     |     | 1.0   | μΑ    |

|                                   |                       | $V_{DS}=60V, V_{GS}=0, T_{j}=125^{\circ}C$ |     |     | 0.5   | mA    |

| Gate Body Leakage Forward         | I <sub>GSSF</sub>     | $V_{DS}=0, V_{GS}=20V$                     |     |     | 100   | nA    |

| Gate Body Leakage Reverse         | $I_{GSSR}$            | $V_{DS} = 0, V_{GS} = -20V$                |     |     | - 100 | nA    |

| Gate Threshold Voltage            | *V <sub>GS (th)</sub> | $V_{DS}=V_{GS}$ , $I_{D}=250\mu A$         | 1.0 |     | 2.5   | V     |

| Static Drain Source On Resistance | *R <sub>DS (on)</sub> | $V_{GS}$ =10V, $I_{D}$ =500mA              |     |     | 7.5   | Ω     |

| Drain Source On Voltage           | *V <sub>DS (on)</sub> | $V_{GS}$ =10V, $I_{D}$ =500mA              |     |     | 3.75  | V     |

|                                   |                       | $V_{GS}=5V$ , $I_D=50mA$                   |     |     | 1.5   | V     |

| On State Drain Current            | *I <sub>D (on)</sub>  | $V_{GS}=10V, V_{DS} \ge 2V_{DS (on)}$      | 500 |     |       | mA    |

| Forward Transconductance          | *G <sub>FS</sub>      | $V_{GS}$ >2V, $V_{DS (on)}$ , $I_D$ =200mA | 80  |     |       | mS    |

#### **DYNAMIC CHARACTERISTICS**

| Input Capacitance            | C <sub>ISS</sub> |                                                     |  | 50  | pF |

|------------------------------|------------------|-----------------------------------------------------|--|-----|----|

| Output Capacitance           | C <sub>OSS</sub> | $V_{DS}$ =25V, $V_{GS}$ =0V, f=1MHz                 |  | 25  | pF |

| Reverse Transfer Capacitance | $C_{RSS}$        |                                                     |  | 5.0 | pF |

| Turn On Time                 | t <sub>on</sub>  | $V_{DD}$ =30V, $R_L$ =25 $\Omega$ ,                 |  | 20  | ns |

| Turn Off Time                | t <sub>off</sub> | $I_D$ =500mA, $V_{GS}$ =10V, $R_{GEN}$ =25 $\Omega$ |  | 20  | ns |

\*Pulse Test: Pulse Width < 300ms, Duty Cycle < 2%

## **SOT-23** Formed SMD Package

### **SOT-23 Formed SMD Package**

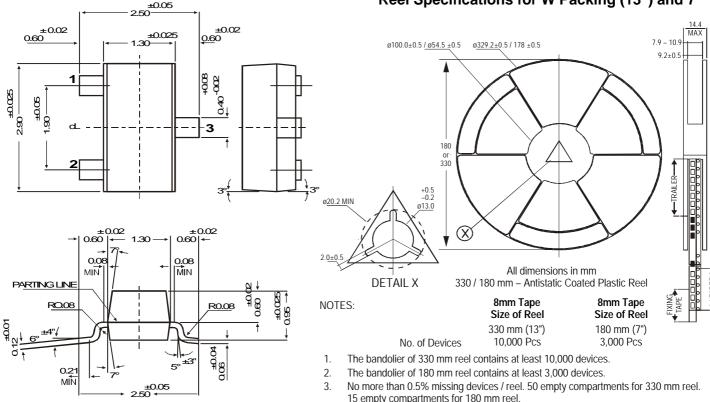

## **SOT-23 Package Reel Information** Reel Specifications for W Packing (13") and 7"

- 15 empty compartments for 180 mm reel.

- Three consecutive empty places might be found provided this gap is followed by 6 consecutive devices.

- The carrier tape (leader) starts with at least 75 empty positions (equivalent to 330 mm). In order to fix the carrier tape a self adhesive tape of 20 to 50 mm is applied. At the end of the bandolier at least 40 empty positions (equivalent to 160 mm) are there.

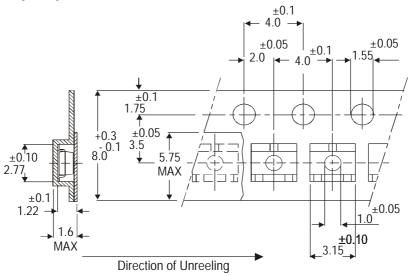

### **Tape Specification for SOT-23 Surface Mount Device**

# **Packing Detail**

All dimensions in mm

| PACKAGE    | STANDARD PACK        |                | INNER CARTON BOX |      | OUTER CARTON BOX  |       |        |

|------------|----------------------|----------------|------------------|------|-------------------|-------|--------|

|            | Details              | Net Weight/Qty | Size             | Qty  | Size              | Qty   | Gr Wt  |

| SOT-23 T&R | 3K/reel 136 gm/3K pc |                | 3" x 7.5" x 7.5" | 12 K | 17" x 15" x 13.5" | 192 K | 12 kgs |

|            |                      |                | 9" x 9" x 9"     | 51 K | 19" x 19" x 19"   | 408 K | 28 kgs |

|            | 10K/reel             | 415 gm/10K pcs | 13" x 13" x 0.5" | 10 K | 17" x 15" x 13.5" | 300 K | 16 kgs |

Customer Notes 2N7002

SOT-23 Formed SMD Package

### **Disclaimer**

The product information and the selection guides facilitate selection of the CDIL's Discrete Semiconductor Device(s) best suited for application in your product(s) as per your requirement. It is recommended that you completely review our Data Sheet(s) so as to confirm that the Device(s) meet functionality parameters for your application. The information furnished in the Data Sheet and on the CDIL Web Site/CD is believed to be accurate and reliable. CDIL however, does not assume responsibility for inaccuracies or incomplete information. Furthermore, CDIL does not assume liability whatsoever, arising out of the application or use of any CDIL product; neither does it convey any license under its patent rights nor rights of others. These products are not designed for use in life saving/support appliances or systems. CDIL customers selling these products (either as individual Discrete Semiconductor Devices or incorporated in their end products), in any life saving/support appliances or systems or applications do so at their own risk and CDIL will not be responsible for any damages resulting from such sale(s).

CDIL strives for continuous improvement and reserves the right to change the specifications of its products without prior notice.

CDIL is a registered Trademark of

Continental Device India Limited

C-120 Naraina Industrial Area, New Delhi 110 028, India.

Telephone + 91-11-2579 6150, 5141 1112 Fax + 91-11-2579 5290, 5141 1119

email@cdil.com www.cdilsemi.com